最先端半導体の国産化を目指すラピダスの小池淳義社長は19日「(最先端チップを載せる)基板の重要部分が完成した」と語り、完成したばかりの試作品を公開した。人工知能(AI)半導体を載せ、チップ同士を効率よくつなぐ。「(米エヌビディアの)ジェンスン・ファン氏のチップを載せたいと願っている」とエヌビディアからの製造受託に意欲を示した。

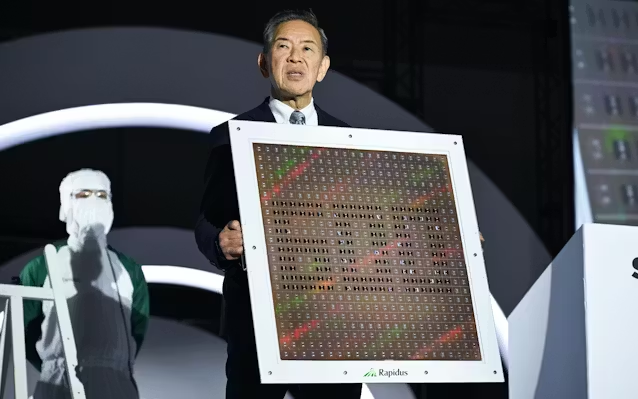

東京ビッグサイト(東京・江東)で開幕中の半導体の国際展示会「セミコン・ジャパン2025」で同日講演し、AI半導体用の配線層「RDLインターポーザー」を公開した。600ミリメートル角のガラス製パネル上に配線層が載り「600」の形になるようにチップを載せた。小池氏は「たくさんのチップが載り、効率よく安価に生産できる」と語った。

エヌビディアのファン最高経営責任者(CEO)は自社の半導体を抱えて登壇する姿で知られる。小池氏は講演中にたびたびファン氏について触れ、自身もパネルを抱えてみせた。ラピダスはエヌビディアなどのAI半導体メーカーからの製造受託を目指している。「このパネルを持つために毎日腕立て伏せを100回やった」と笑いを誘った。

インターポーザーは通常は直径300ミリの丸形のウエハーから切り出してつくるが、ラピダスは600ミリ角のパネルから取り出す。1枚から取れる数は49個と、ウエハーから取るよりも10倍以上に増えるためAI半導体の製造コストを抑えられる。

AI半導体は性能進化により「だんだんデバイスが大きくなっている」(小池社長)と言い、ラピダスは配線層のサイズも他社より1.3〜2倍程度に高めた。28年に組み立て工程の量産開始を目指している。

【関連記事】

- ・ラピダス、AI半導体向け基板の生産効率10倍に TSMC対抗へ試作成功

- ・AI普及でカギ握る半導体組み立て 富士フイルムやレゾナックが新素材

- ・ラピダスへの民間融資、債務の最大8割を政府保証 経産省

鄭重声明:本文の著作権は原作者に帰属します。記事の転載は情報の伝達のみを目的としており、投資の助言を構成するものではありません。もし侵害行為があれば、すぐにご連絡ください。修正または削除いたします。ありがとうございます。